Blog Credit: Trupti Thakur

Image Courtesy: Google

RISC-V CHIP

Wearable devices, such as smartwatches and pulse oximeters, are gaining popularity with the continuous expansion of IoT applications in recent years. However, the diverse systems and network protocols required lead to high software migration costs and inconsistent security levels This poses challenges to the healthy development of the wearables industry.

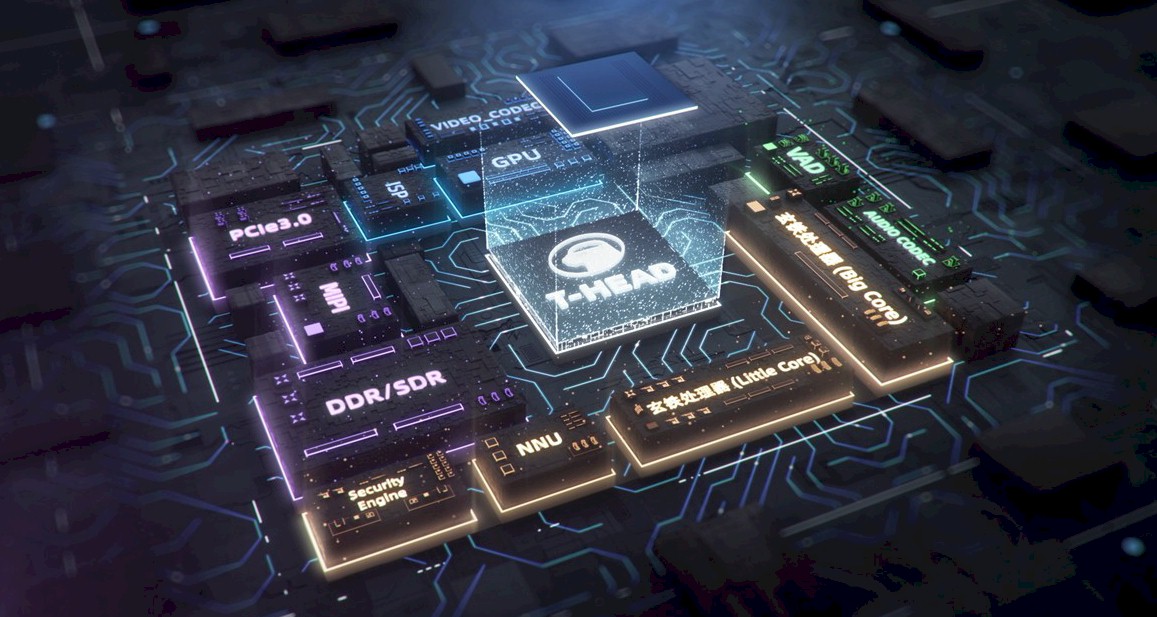

At the inaugural XuanTie RISC-V Ecosystem Conference, a secure payment solution featuring cloud-device integration was unveiled to tackle these issues. Collaboratively launched by T-Head, Alipay, and the China Academy of Information and Communications Technology (CAICT), this innovative offering establishes a new standard for wearable payment devices. Dubbed as “wearable payment security solution”, it has effectively bridging the gap in the industry. It marks a significant milestone for wearable devices and lays a strong foundation for future development. Moreover, Alipay has introduced its “Payment Chip” program to develop secure payment capabilities in cooperation with manufacturers. T-Head and Alipay will join hands to roll out the first batch of Made-In-China chips with secure payment.

In terms of chip design, payment chips powered by T-Head RISC-V CPUs offer more than cost savings. They are highly customizable to various application scenarios, making them an ideal choice for IoT devices. More importantly, these payment chips are designed to offer top-notch, hardware-based security that extends deep into the processor cores of wearable payment devices.

The solution provides a complete Turnkey method to secure wearable payments, supporting both SE and TEE security levels. Based on the secure software architecture of T-Head, these two security schemes can be quickly imported by leveraging a unified migration interface that is extensible and user-friendly. This greatly minimizes the software migration, as well as development costs for solution providers.

TEE technologies are primarily employed in high-performance and -security scenarios. T-Head’s Virtual Zone security technology offers a highly secure runtime environment for applications that is compatible with Global Platform TEE security technologies. This enables seamless and secure application migration from other platforms to payment chips. By combining T-Head’s TEE with SE security technologies, we succeeded to fit in most of the secure IoT application scenarios while meeting the security standards of various industries and regions.

The solution employs stringent hardware and software security measures to prevent theft or cloning of users’ payment assets which are stored in the protected and isolated memory of security chips. Additionally, the key code used for generating payment tokens also runs in a secure execution environment, improving the security of wearable payments even more extensively.

The wearable payment security solution offers significant benefits to low and medium-end wearable watch solution providers, providing them with cost-effective and highly secure payment capabilities. This has a significant impact on the payment industry, and has the potential to expand to other industries as well. T-Head’s XuanTie security technologies made it possible for replicable and extensible security schemes to be implemented in different payment scenarios, creating a more comprehensive software ecosystem for using RISC-V chips in wearable devices.

About RISC-V technology

- It is an open-source technology that is pronounced “risk five”.

- It is an open-source instruction set architecture(ISA) used for the development of custom processors targeting a variety of end applications.

- It is considered the fifth generation of processors built on the concept of the reduced instruction set computer (RISC).

- It was begun as a project at UC Berkeley to create an open-source computer system based on RISC principles.

- It was initially designed for academic use. The standard has evolved and is now managed by RISC-V International. How Does RISC-V Work?

- As an open-standard architecture, RISC-V is defined by member companies of RISC-V International, the global nonprofit organization behind the ISA.

- The intent is that through collaboration, the member companies can contribute to new avenues of processor innovationwhile promoting new degrees of design freedom.

- It features a small core set of instructions upon which all the design’s software runs.

- The architecture allows designers to customize and build their processorin a way that’s tailored to their target end applications.

- Benefits of RISC-V include:

- Its open-standard nature, which allows collaborationand innovation across the industry.

- The entire RISC-V architecture can be scrutinized closelyin the public domain, eliminating back doors and hidden channels.

- Applications: Wearables, Industrial, IoT, and Home Appliances, Smartphones, Automotive, High-Performance Computing (HPC), and Data Centers.

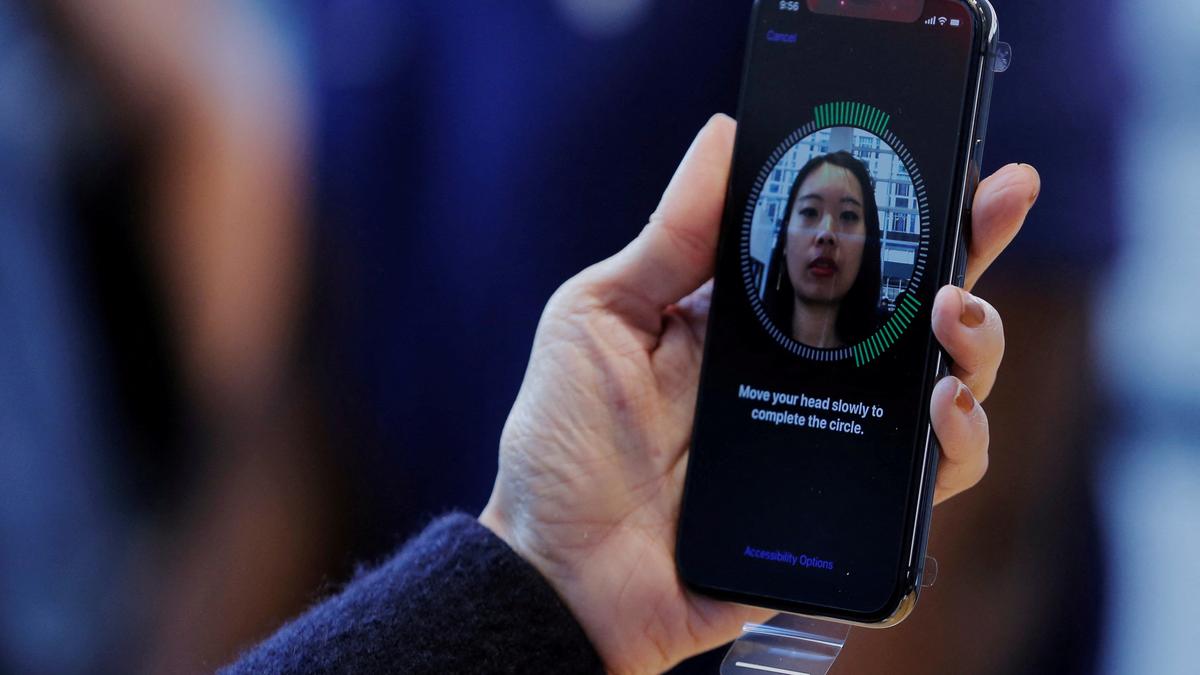

As The Chip designer Qualcomm said on Tuesday it is partnering with Alphabet’s Google to make wearable devices like smartwatches using chips based on RISC-V technology.

RISC-V, pronounced as “risk five,” is an open-source technology that competes with costly proprietary technology from British chip designer Arm Holdings .

RISC-V can be used as a key ingredient for anything from a smartphone chip to advanced processors for artificial intelligence.

US companies are still actively working to advance RISC-V based technology despite concerns expressed by lawmakers that China is exploiting a culture of open collaboration among American companies to advance its own semiconductor industry.

Qualcomm said it plans to commercialize the RISC-V-based wearables solution globally including the United States.

It would help more products within the Android ecosystem to take advantage of custom processors that are low power and high performance, Qualcomm said.

Blog By: Trupti Thakur

20

OctRISC-V Chip

Oct 20, 2023Recent Blog

India’s Steps Into 6GMay 15, 2025

The New Accessibility Feature of AppleMay 14, 2025

The Digital Threat Report 2024May 13, 2025

The MADMAX ExperimentMay 12, 2025

The EntraID Data ProtectionMay 10, 2025